# CMS8S78xx series Reference Manual

Enhanced flash 8-bit 1T 8051 microcontroller Rev. 1.0.8

Please be reminded about following CMS's policies on intellectual property

<sup>\*</sup> Cmsemicron Limited(denoted as 'our company' for later use) has already applied for relative patents and entitled legal rights. Any patents related to CMS's MCU or other producrts is not authorized to use. Any individual, organization or company which infringes s our company's interlectual property rights will be Disableand stopped by our company through any legal actions, and our company will claim the lost and required for compensation of any damage to the company.

<sup>\*</sup> The name of Cmsemicron Limited and logo are both trademarks of our company.

<sup>\*</sup> Our company preserve the rights to further elaborate on the improvements about products' function, reliability and design in this manual. However, our company is not responsible for any usage about this munal. The applications and their purposes in this manual are just for clarification, our company does not guarantee that these applications are feasible without further improvements and changes, and our company does not recommend any usage of the products in areas where people's safety is endangered during accident. Our company's products are not authorzed to be used for life-saving or life support devices and systems.our company has the right to change or improve the product without any prior notification, for latest news, please visit our website: www.mcu.com.cn

# **Table of Content**

| CMS8   | S78xx series                              | 1  |

|--------|-------------------------------------------|----|

| 1. Ce  | entral Processing Unit (CPU)              | 11 |

| 1.1    | Reset Vector (0000H)                      | 11 |

| 1.2    | BOOT Partition                            |    |

| 1.3    | Accumulator (ACC)                         | 13 |

| 1.4    | B Register(B)                             |    |

| 1.5    | Stack Pointer Register (SP)               |    |

| 1.6    | Data Pointer Register (DPTR0/DPTR1)       |    |

| 1.7    | Data Pointer Selection Register (DPS)     | 14 |

| 1.8    | Program Status Register (PSW)             | 14 |

| 1.9    | Program Counter (PC)                      | 15 |

| 1.10   | Timing Access Register (TA)               | 15 |

| 2. Me  | emory and Register Mapping                | 16 |

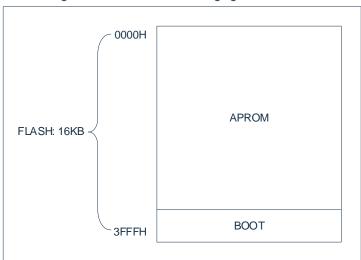

| 2.1    | Program Storage Flash                     | 16 |

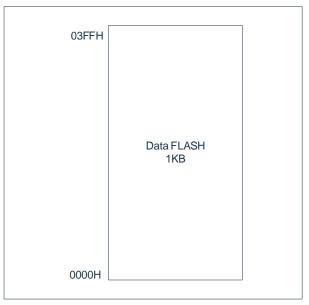

| 2.2    | Non-volatile Data Memory Data FLASH       | 17 |

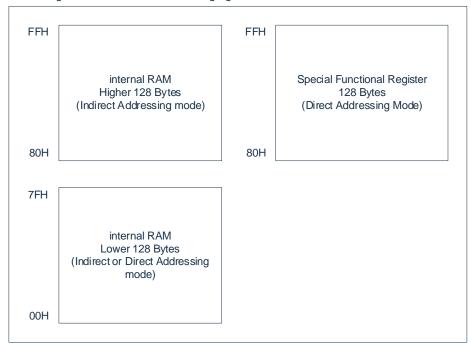

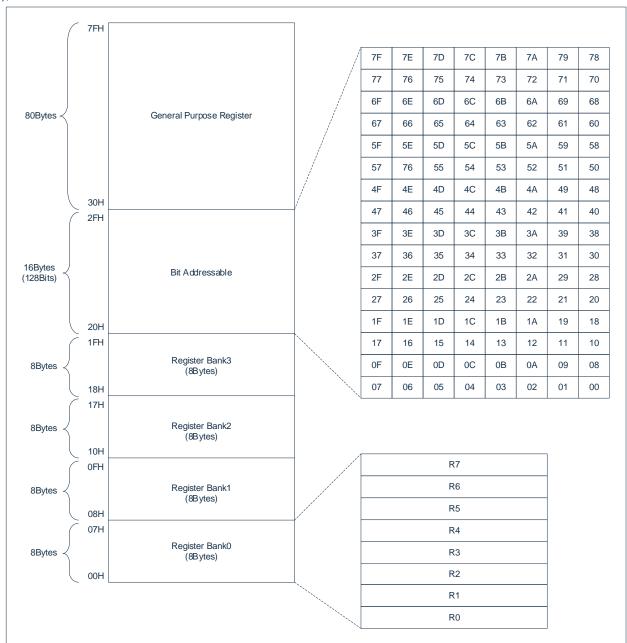

| 2.3    | General Data Register RAM                 | 17 |

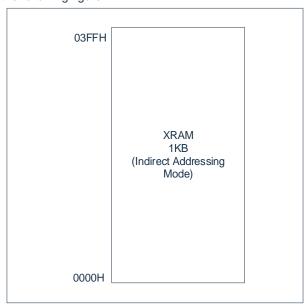

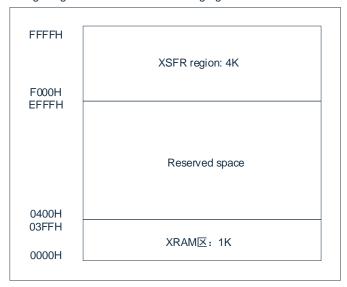

| 2.4    | General External Data Register XRAM       | 19 |

| 2.5    | Special Function Register SFR             | 20 |

| 2.6    | External Special Function Register XSFR   | 21 |

| 3. Re  | eset                                      | 27 |

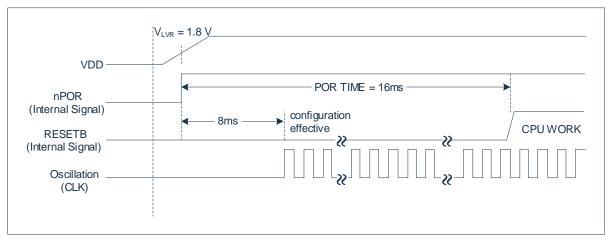

| 3.1    | Power-on Reset                            | 27 |

| 3.2    | External Reset                            | 29 |

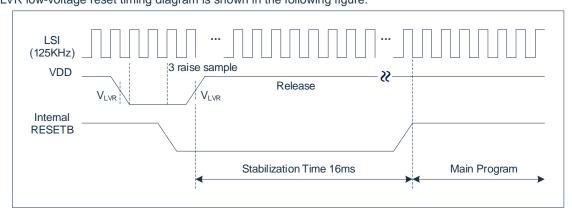

| 3.3    | LVR Low-voltage Reset                     | 29 |

| 3.4    | Watchdog Reset                            | 30 |

| 3.5    | Software Reset                            |    |

| 3.6    | CONFIG Status Protection Reset            | 30 |

| 3.7    | Power-on Configuration Monitor Reset      | 31 |

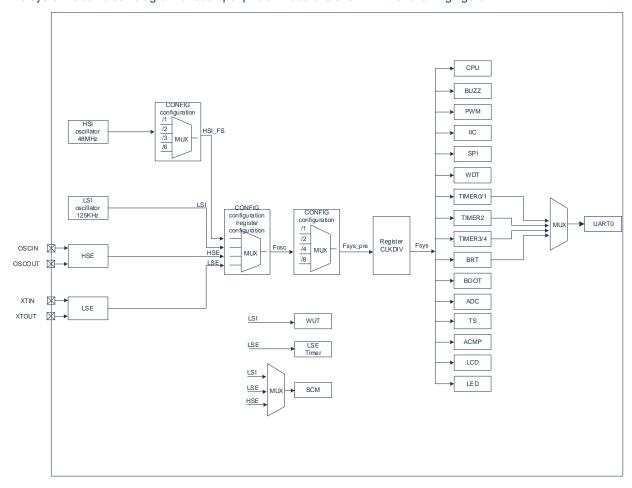

| 4. Clo | ock Structure                             | 32 |

| 4.1    | System Clock Structure                    |    |

| 4.2    | Related Registers                         | 33 |

| 4.2.   | .1 Oscillator Control Register CLKDIV     | 33 |

| 4.2.   | .2 System Clock Switching Register SCKSEL | 33 |

| 4.2.   | .3 System Clock Status Register SCKSTAU   | 34 |

| 4.2.   | .4 System Clock Monitor Register SCM      | 35 |

| 4.2.   | .5 Function Clock Control Registers       | 36 |

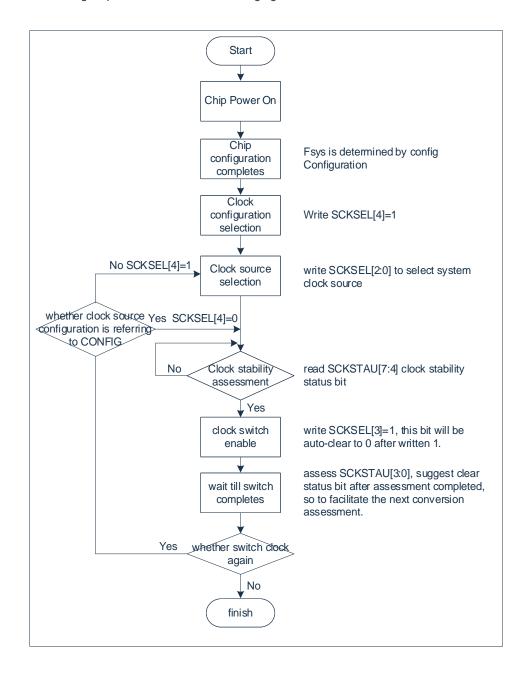

| 4.3    | System clock switching                    |    |

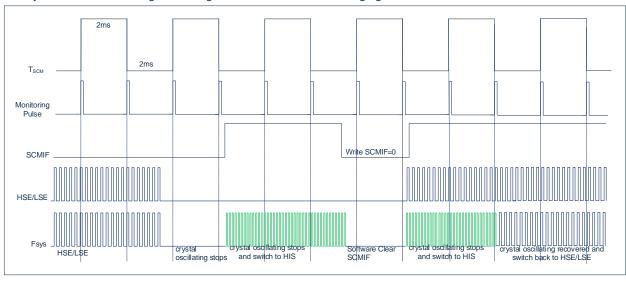

| 4.4    | System Clock Monitoring                   | 38 |

| 5. Po  | wer Management                            | 39 |

| 5.1    | Power Management Register PCON            | 39 |

| 5.2    | Power Supply Monitor Register LVDCON      | 40 |

| 5.3    | IDLE Idle Mode                            | 40 |

| 5.4    | STOP Sleep Mode                           | 41 |

| 5.4.   | .1 Sleep Wakes up                         | 41 |

| 5.4.   | .2 Wake-up Wait State                     | 41 |

| 5.4.   | .3 Sleep Wake-up Time                     | 41 |

| 5.4.   | ·                                         |    |

| 5.4.   | .5 Sleep Power Consumption in Debug Mode  | 42 |

|    | 5.4.6 | Example of a Sleep Mode Application               | 42 |

|----|-------|---------------------------------------------------|----|

| 6. | Inter | rrupt                                             | 43 |

| 6  | .1 I  | nterrupt Overview                                 | 43 |

| 6  | .2 E  | External Interrupts                               | 44 |

|    | 6.2.1 | INT0/INT1 Interrupt                               | 44 |

|    | 6.2.2 | GPIO Interrupt                                    | 44 |

| 6  | .3 I  | nterrupt With Sleep Wake-up                       | 44 |

| 6  | .4 I  | nterrupt Register                                 | 45 |

|    | 6.4.1 | Interrupt Mask Registers                          | 45 |

|    | 6.4.2 | Interrupt Priority Controls the Register          | 49 |

|    | 6.4.3 | Interrupt Flag Bit Register                       |    |

|    | 6.4.4 | The clear operation for the interrupt flag bit    |    |

|    | 6.4.5 | Special Interrupt Flag Bits in Debug Mode         | 59 |

| 7. | I/O F | Port                                              | 60 |

| 7  | .1 (  | GPIO Function                                     | 60 |

|    | 7.1.1 | PORTx Data Register Px                            | 60 |

|    | 7.1.2 | PORTx Direction Register PxTRIS                   | 60 |

|    | 7.1.3 | PORTx Open-drain Control Register PxOD            | 61 |

|    | 7.1.4 | PORTx Pull-up Resistor Control Register PxUP      | 61 |

|    | 7.1.5 | PORTx pull-down resistor control register PxRD    |    |

|    | 7.1.6 | PORTx Slope Control Register PxSR                 | 62 |

|    | 7.1.7 | The PORTx Data Input Selects Register PxDS        |    |

| 7  | .2    | Multiplexed Functions                             |    |

|    | 7.2.1 | Port multiplexing feature table                   |    |

|    | 7.2.2 | Port Multiplexing Feature Configuration Register  |    |

|    | 7.2.3 | The Port Input Function Allocation Registers      |    |

|    | 7.2.4 | Communication Input Function Allocation Registers |    |

|    | 7.2.5 | Port external interrupt control registers         |    |

|    | 7.2.6 | Multiplexing Features Application Notes           |    |

| 8. | Wate  | chdog Timer (WDT)                                 | 70 |

| 8  | .1 (  | Overview                                          | 70 |

| 8  | .2 F  | Related Registers                                 | 70 |

|    | 8.2.1 | Watchdog Control Register WDCON                   | 70 |

|    | 8.2.2 | Watchdog overflow control register CKCON          |    |

| 8  | .3 ۱  | WDT Interrupt                                     |    |

|    | 8.3.1 | Interrupt Mask Register EIE2                      |    |

|    | 8.3.2 | Interrupt priority control register EIP2          | 73 |

| 9. | Time  | er Counter 0/1 (Timer0/1)                         | 74 |

| 9  | .1 (  | Overview                                          | 74 |

| 9  | .2 F  | Related Registers                                 | 75 |

|    | 9.2.1 | Timer0/1 mode register TMOD                       | 75 |

|    | 9.2.2 | Timer0/1 control register TCON                    | 76 |

|    | 9.2.3 | Timer0 data register low bit TL0                  | 76 |

|    | 9.2.4 | Timer0 data register high bit TH0                 | 77 |

|    | 9.2.5 | Timer1 data register low bit TL1                  | 77 |

|    | 9.2.6 | Timer1 data register high TH1                     |    |

|    | 9.2.7 | Function clock control register CKCON             | 77 |

| 9  | .3    | Timer0/1 Interrupt                                | 78 |

|    | 9.3.1 | Interrupt Mask register IE                        |    |

|    | 9.3.2 | Interrupt priority control register IP            | 79 |

|          | Timer0/1, INT0/1 interrupt flag bit register TCON           |     |

|----------|-------------------------------------------------------------|-----|

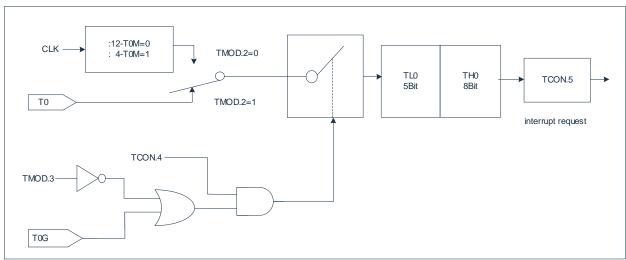

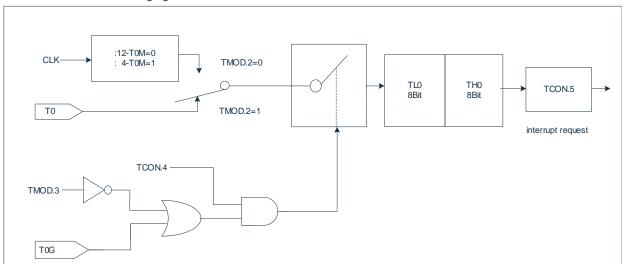

| 9.4 T    | imer0 Working Mode                                          |     |

| 9.4.1    | T0 - Mode 0 (13-bit Timing/Counting Mode)                   | 81  |

| 9.4.2    | T0 - Mode 1 (16-bit Timing/Counting Mode)                   | 81  |

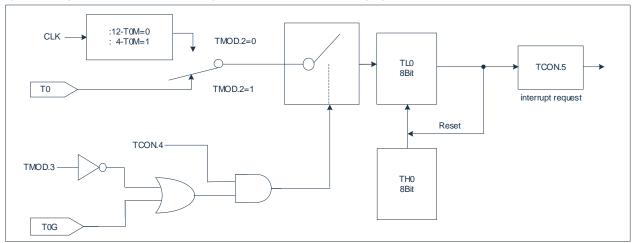

| 9.4.3    | T0 - Mode 2 (8-bit Auto-reload Timing/Counting Mode)        | 82  |

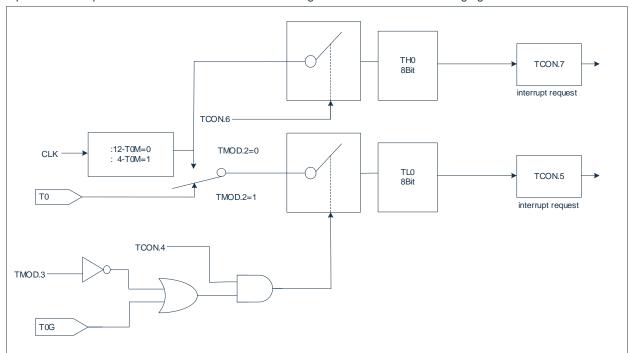

| 9.4.4    | T0 - Mode 3 (Two Separate 8-bit Timers/Counters)            | 82  |

| 9.5 T    | imer1 Working Mode                                          | 83  |

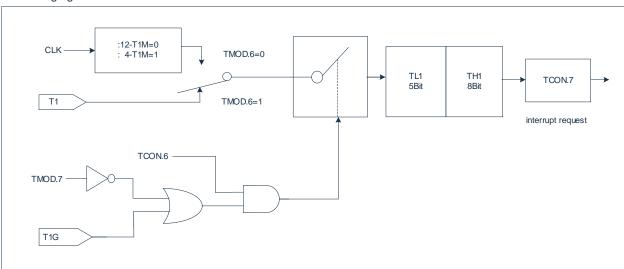

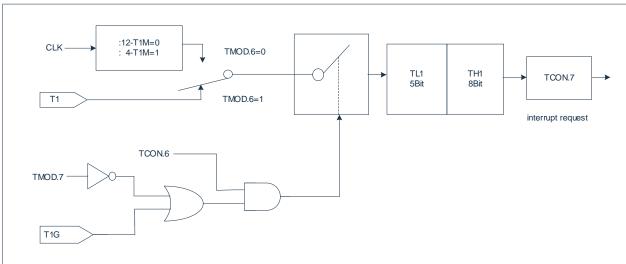

| 9.5.1    | T1 - Mode 0 (13-bit Timing/Counting Mode)                   | 83  |

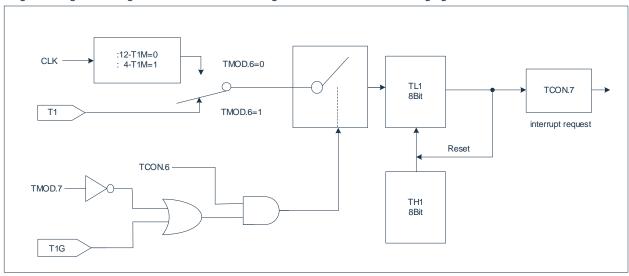

| 9.5.2    | T1 - Mode 1 (16-bit Timing/Counting Mode)                   | 83  |

| 9.5.3    | T1 - Mode 2 (8-bit Auto Reload Timing/Counting Mode)        | 84  |

| 9.5.4    | T1 - Mode 3 (Stop Count)                                    | 84  |

| 10. Time | er Counter 2 (Timer2)                                       | 85  |

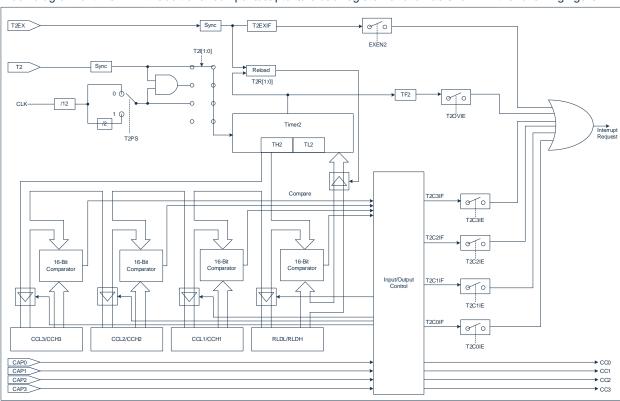

|          | Overview                                                    |     |

|          | Related Registers                                           |     |

|          | Timer2 Control Register T2CON                               |     |

|          | Timer2 Data Register Low Bit TL2                            |     |

|          | Timer2 Data Register High Bit TH2                           |     |

|          | Timer2 Compare/Capture/Auto Reload Register Low Bit RLDL    |     |

|          | Timer2 Compare/Capture/Auto Reload Register High Bit RLDH   |     |

|          | Timer2 Compares/Captures Channel 1 Register Low-bit CCL1    |     |

|          | Timer2 Compares/Captures Channel 1 Register High-bit CCH1   |     |

|          | Timer2 Compares/Captures Channel 2 Register Low-bit CCL2    |     |

|          | Timer2 Compares/Captures Channel 2 Register High-bit CCH2   |     |

|          | 0 Timer2 Compares/Captures Channel 3 Register Low-bit CCL3  |     |

|          | 1 Timer2 Compares/Captures Channel 3 Register High-bit CCH3 |     |

|          | 2 Timer2 Compares the Capture Control Register CCEN         |     |

|          | imer2 Interrupts                                            |     |

|          | Interrupt Correlation Registers                             |     |

|          | Timer Interrupts                                            |     |

|          | Externally Triggered Interrupts                             |     |

|          | Compare Interrupts                                          |     |

|          | Capture Interrupts                                          |     |

|          | imer2 Feature Description                                   |     |

|          | Timing Mode                                                 |     |

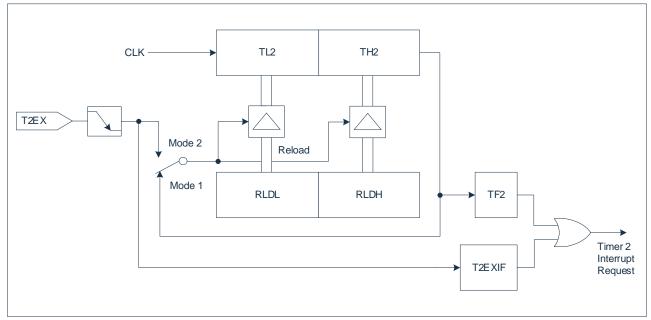

|          | Reload Mode                                                 |     |

|          | Gated Timing Mode                                           |     |

|          | Event Counting Mode                                         |     |

|          | <u> </u>                                                    |     |

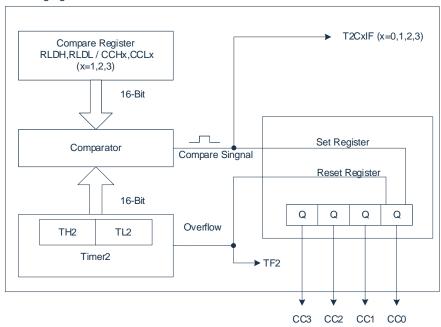

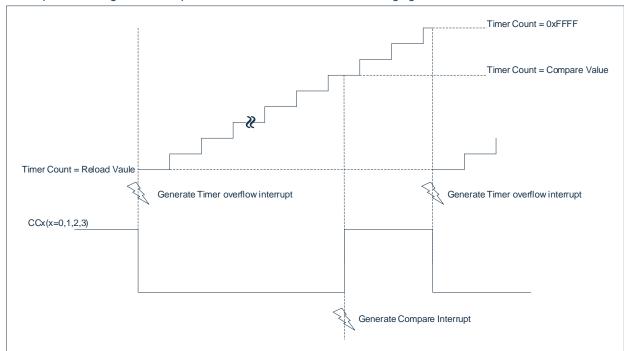

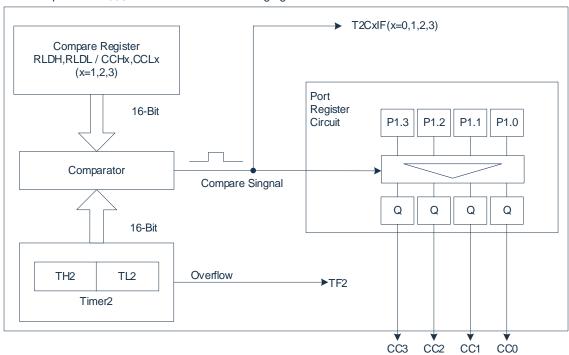

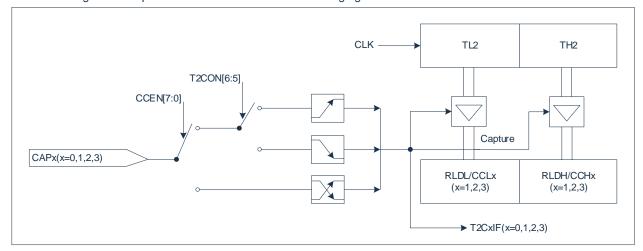

|          | Compare Mode                                                |     |

|          | ·                                                           |     |

|          | er 3/4 (Timer3/4)                                           |     |

|          | Overview                                                    |     |

|          | Related Registers                                           |     |

|          | Timer3/4 Control Register T34MOD                            |     |

|          | Timer3 data register low bit TL3                            |     |

|          | Timer3 data register high bit TH3                           |     |

|          | Timer4 data register low bit TL4                            |     |

|          | Timer4 data register high bit TH4                           |     |

|          | imer3/4 Interrupt                                           |     |

|          | Interrupt mask register EIE2                                |     |

|          | Interrupt Priority Control Register EIP2                    |     |

| 11.3.3   | Peripheral Interrupt Flag Bit Register EIF2                 | 105 |

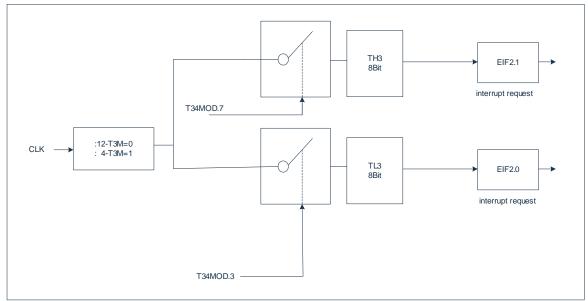

| 11.4 Timer3 Working Mode                                             |     |

|----------------------------------------------------------------------|-----|

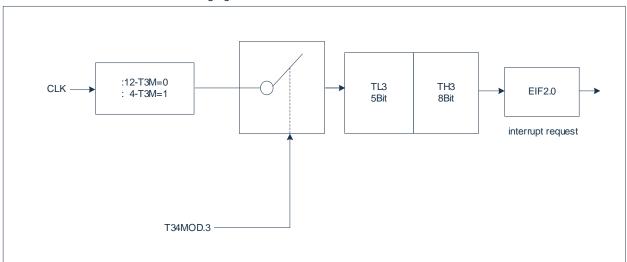

| 11.4.1 T3 - Mode 0 (13-bit Timing Mode)                              | 106 |

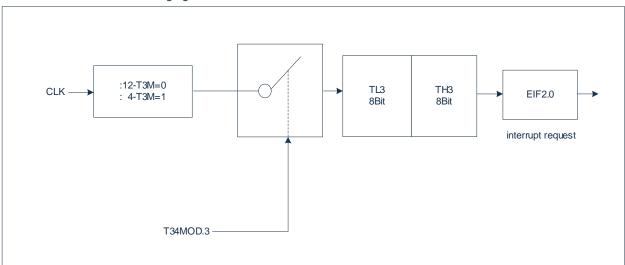

| 11.4.2 T3 - Mode 1 (16-bit Timing Mode)                              | 106 |

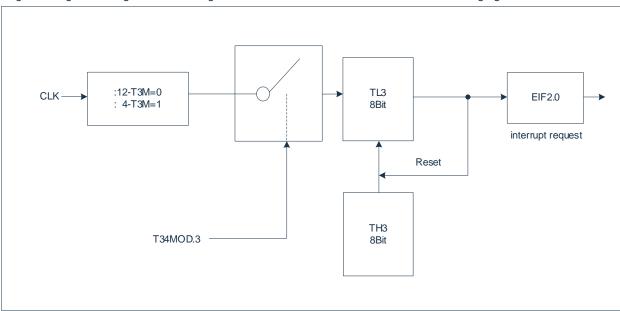

| 11.4.3 T3 - Mode 2 (8-bit Auto Reload Timing Mode)                   | 107 |

| 11.4.4 T3 - Mode 3 (Two Separate 8-bit Timers)                       | 107 |

| 11.5 Timer4 Working Mode                                             |     |

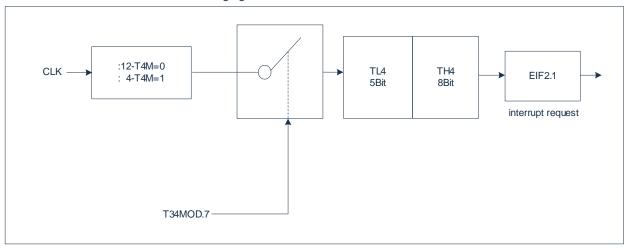

| 11.5.1 T4 - Mode 0 (13-bit Timing Mode)                              | 108 |

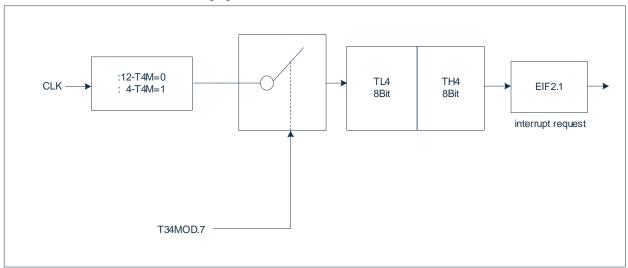

| 11.5.2 T4 - Mode 1 (16-bit timing mode)                              | 108 |

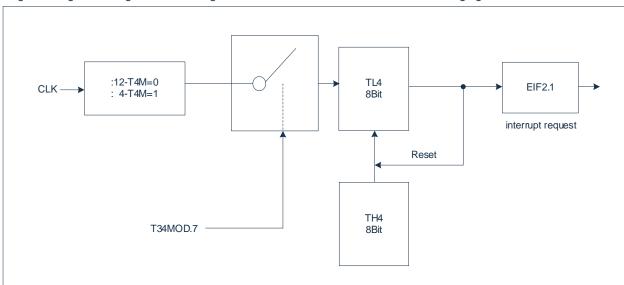

| 11.5.3 T4- Mode 2 (8-bit auto Reload Timing Mode)                    | 109 |

| 11.5.4 T4 - Mode 3 (Stop Count)                                      | 109 |

| 12. LSE Timer(LSE_Timer)                                             | 110 |

| 12.1 Overview                                                        | 110 |

| 12.2 Related Registers                                               | 110 |

| 12.2.1 LSE Timer Data Register Low 8 bit LSECRL                      | 110 |

| 12.2.2 LSE Timer Data Registers are 8 Bits High LSECRH               | 110 |

| 12.2.3 LSE Timer Control Register LSECON                             | 111 |

| 12.3 Interrupt With Sleep Wake-up                                    | 112 |

| 12.4 Feature Description                                             | 112 |

| 13. Wake-up Timer (WUT)                                              | 113 |

| 13.1 Overview                                                        | 113 |

| 13.2 Related Registers                                               | 113 |

| 13.2.1 WUTCRH Register                                               | 113 |

| 13.2.2 WUTCRL Register                                               | 113 |

| 13.3 Feature Description                                             | 114 |

| 14. Baud Rate Timer (BRT)                                            | 115 |

| 14.1 Overview                                                        | 115 |

| 14.2 Related Registers                                               |     |

| 14.2.1 BRT Module Control Register BRTCon                            |     |

| 14.2.2 The BRT Timer Data is Loaded With a Low 8-bit Register BRTDL  | 115 |

| 14.2.3 The BRT Timer Data is Loaded With a High 8-bit Register BRTDH | 115 |

| 14.3 Feature Description                                             | 116 |

| 15. Buzzer Driver (BUZZER)                                           | 117 |

| 15.1 Overview                                                        | 117 |

| 15.2 Related Registers                                               |     |

| 15.2.1 BUZZER Control Register BUZCON                                | 117 |

| 15.2.2 BUZZER Frequency Control Register BUZDIV                      | 117 |

| 15.3 Feature Description                                             |     |

| 16. Enhanced PWM Module                                              | 119 |

| 16.1 Overview                                                        | 119 |

| 16.2 Characteristic                                                  |     |

| 16.3 Port Configuration                                              |     |

| 16.4 Feature Description                                             |     |

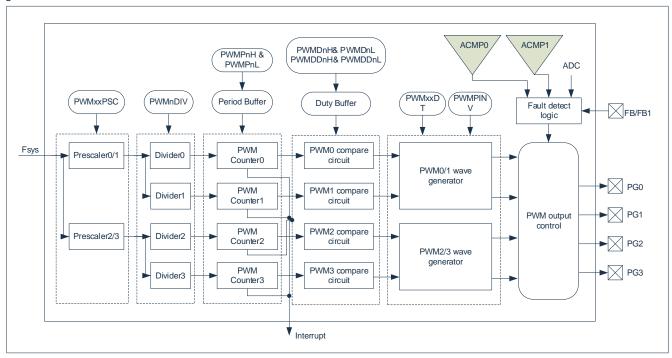

| 16.4.1 Functional Block Diagram                                      |     |

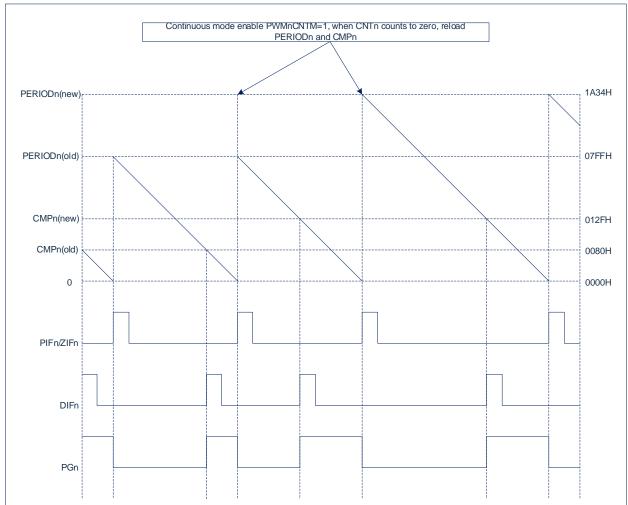

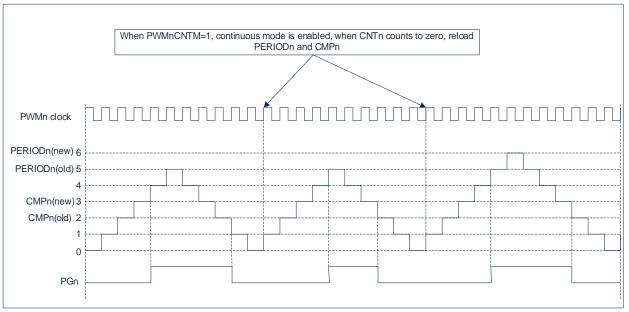

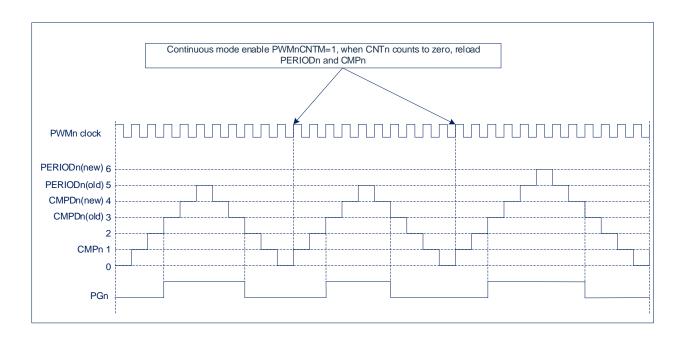

| 16.4.2 Edge Alignment                                                |     |

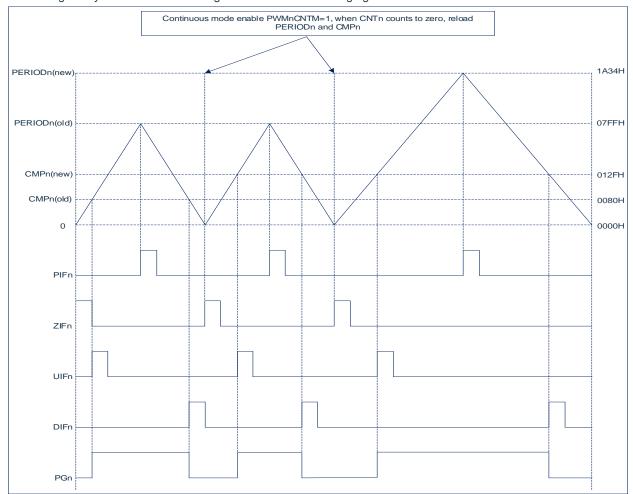

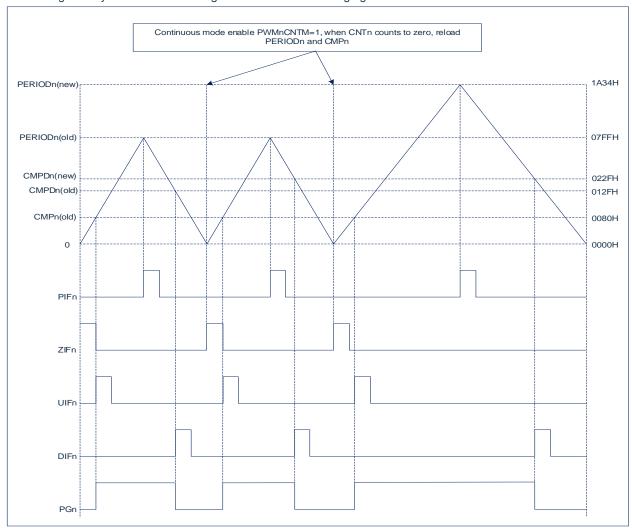

| 16.4.3 Center alignment                                              |     |

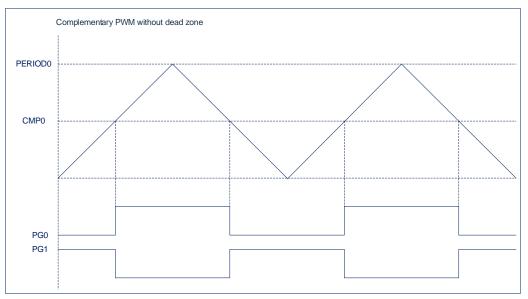

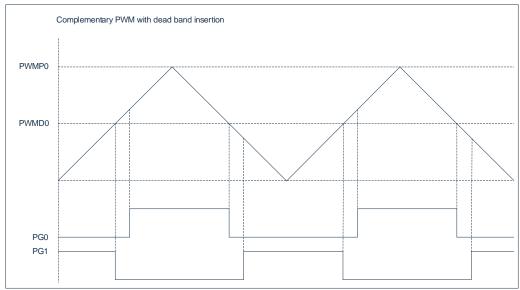

| 16.4.4 Complementary Model                                           |     |

| 16.4.5 Synchronous Mode                                              |     |

| 16.4.6 Mask Output                                                   | 127 |

| 16.4.7 Brake Function                                                | 127 |

| 16.5 P\ | WM-related Registers                                        | 130 |

|---------|-------------------------------------------------------------|-----|

|         | PWM Control Register PWMCON                                 |     |

| 16.5.2  | PWM Output Enable Control Register PWMOE                    | 130 |

| 16.5.3  | PWM0/1 Clock Prescale Control Register PWM01PSC             | 131 |

| 16.5.4  | PWM2/3 Clock Prescale Control Register PWM23PSC             | 131 |

| 16.5.5  | PWM Clock Divider Control Register PWMnDIV (n=0-3).         | 131 |

| 16.5.6  | PWM Data Loading Enable Control Register PWMLOADEN          | 132 |

| 16.5.7  | PWM Output Polarity Control Register PWMPINV                | 132 |

| 16.5.8  | PWM Counter Mode Control Register PWMCNTM                   | 132 |

| 16.5.9  | PWM Counter Enable Control Register PWMCNTE                 | 133 |

| 16.5.10 | PWM Counter Mode Control Register PWMCNTCLR                 | 133 |

| 16.5.11 | PWM Cycle Data Register Low 8 Bits PWMPnL (n=0-3)           | 133 |

| 16.5.12 | PWM Cycle Data Register High 8 Bits PWMPnH (n=0-3)          | 133 |

| 16.5.13 | PWM Compare Data Register Low 8 BitS PWMDnL (n=0-3)         | 134 |

| 16.5.14 | PWM compare 8 bits higher PWMDnH (n=0-3)                    | 134 |

| 16.5.15 | PWM down compare data register 8 bits lower PWMDDnL (n=0-3) | 134 |

| 16.5.16 | PWM down compare data register 8 bits high PWMDDnH (n=0-3)  | 134 |

| 16.5.17 | PWM dead-zone enable control register PWMDTE                | 135 |

|         | PWM0/1 Dead-zone Delay Data Register PWM01DT                |     |

| 16.5.19 | PWM2/3 Dead-zone Delay Data Register PWM23DT                | 135 |

| 16.5.20 | PWM Mask Control Register PWMMASKE                          | 135 |

| 16.5.21 | PWM Mask Data Register PWMMASKD                             | 136 |

|         | PWM Brake Control Register PWMFBKC                          |     |

|         | PWM Brake Recovery Control Register PWMBRKC                 |     |

|         | PWM Delayed Recovery Data Register Low 8 Bit PWMBRKRDTL     |     |

|         | PWM Delayed Recovery Data Register High 2 Bits PWMBRKRDTH   |     |

|         | PWM Brake Data Register PWMFBKD                             |     |

|         | NM Interrupt                                                |     |

|         | Interrupt Mask Register EIE2                                |     |

|         | Interrupt Priority Control Register EIP2                    |     |

|         | PWM Cycle Interrupt Shield Register PWMPIE                  |     |

|         | PWM Zero Interrupt Mask Register PWMZIE                     |     |

|         | PWM up Compare Interrupt Mask Registers PWMUIE              |     |

|         | PWM Down Compare Interrupt Mask Registers PWMDIE            |     |

|         | PWM Cycle Interrupt Flag Register PWMPIF                    |     |

|         | PWM Zero Interrupt Flag Register PWMZIF                     |     |

|         | PWM Up Compare Interrupt Flag Register PWMUIF               |     |

| 16.6.10 | PWM Down Compares Interrupt Flag Register PWMDIF            | 142 |

| 17. LCD | Driver                                                      | 143 |

| 17.1 O  | verview                                                     | 143 |

| 17.2 CI | haracteristic                                               | 143 |

| 17.3 L0 | CD Operating Instructions                                   | 143 |

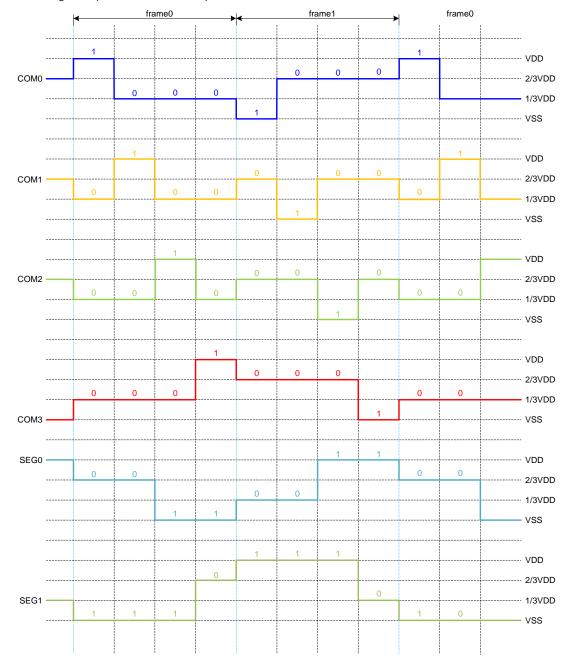

| 17.3.1  | 1/3 Bias Register Operation                                 | 143 |

| 17.3.2  | 1/3 Bias Timing Diagram                                     | 144 |

|         | elated Registers                                            |     |

|         | LCD Control Register LCDCON0                                |     |

|         | LCD COM/SEG Select Register LCD_S0                          |     |

|         | LCD COM/SEG Select Register LCD_S1                          |     |

|         | LCD COM/SEG Select Register LCD_S2                          |     |

|         | LCD Function Select Register LCDEN0                         |     |

| 17.4.6  | LCD Function Select Register LCDEN1                         | 146 |

| 17.4.7  | LCD Function Select Register LCDEN2                         | 146 |

| 18. LED Driver                                                   | 147     |

|------------------------------------------------------------------|---------|

| 18.1 Overview                                                    |         |

| 18.2 Characteristic                                              |         |

| 18.3 Related Registers                                           |         |

| 18.3.1 SEG Port P00-P03 Drive Current Control Register LEDSDRP   | 0L147   |

| 18.3.2 SEG Port P04-P07 Drive Current Control Register LEDSDRP   | 0H147   |

| 18.3.3 SEG Port P10-P13 Drive Current Control Register LEDSDRP   |         |

| 18.3.4 SEG Port P14-P17 Drive Current Control Register LEDSDRP   |         |

| 18.3.5 SEG Port P20-P23 Drive Current Control Register LEDSDRP.  |         |

| 18.3.6 SEG Port P24-P27 Drive Current Control Register LEDSDRP.  |         |

| 18.3.7 SEG Port P30-P33 Drive Current Control Register LEDSDRP   |         |

| 18.3.8 LED COM Port Sink Current Selection Register PnDR (n=0/1/ | 2/3)150 |

| 19. SPI Module                                                   | 151     |

| 19.1 Overview                                                    |         |

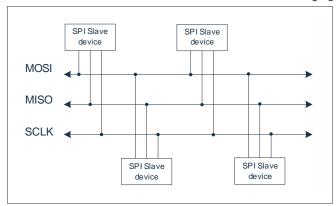

| 19.2 SPI Port Configuration                                      |         |

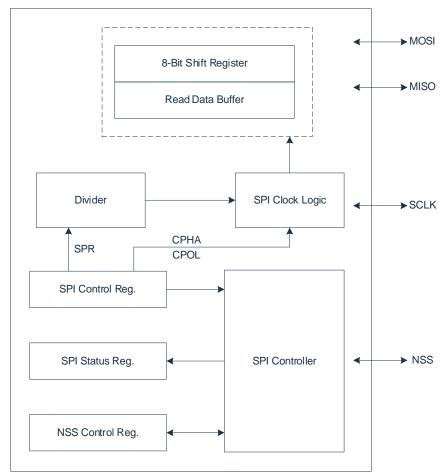

| 19.3 SPI Hardware Description                                    |         |

| 19.4 SPI-related Registers                                       |         |

| 19.4.1 SPI Control Register SPCR                                 | 154     |

| 19.4.2 SPI Data Register SPDR                                    | 154     |

| 19.4.3 SPI Device Select Control Register SSCR                   | 155     |

| 19.4.4 SPI Status Register SPSR                                  |         |

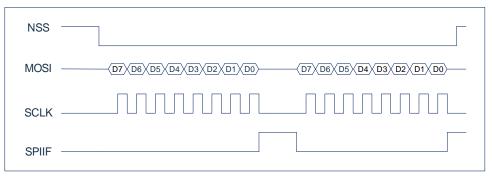

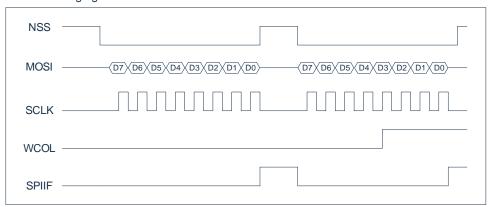

| 19.5 SPI Master Mode                                             |         |

| 19.5.1 Write Conflict Error                                      | 157     |

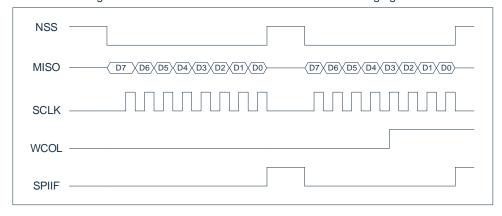

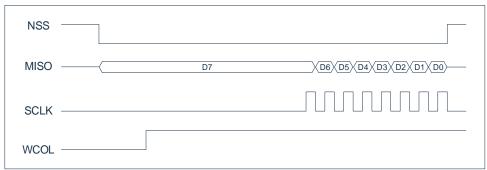

| 19.6 SPI Slave Mode                                              |         |

| 19.6.1 Address Error                                             |         |

| 19.6.2 Write Conflict Error                                      |         |

| 19.7 SPI Clock Control Logic                                     |         |

| 19.7.1 SPI Clock Phase and Polarity Control                      |         |

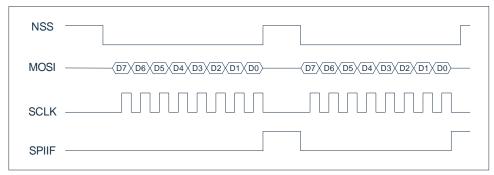

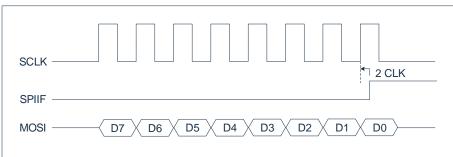

| 19.7.2 SPI Transfer Format                                       |         |

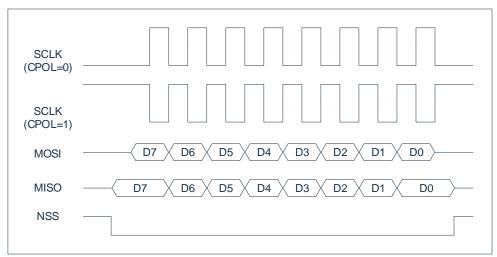

| 19.7.3 CPHA=0 Transfer Format                                    |         |

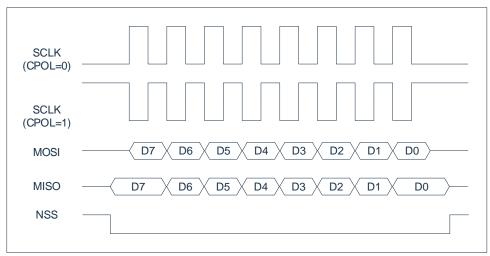

| 19.7.4 CPHA=1 Transfer Format                                    |         |

|                                                                  |         |

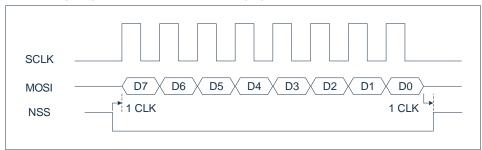

| 19.8.1 SPI Transfer Starts                                       |         |

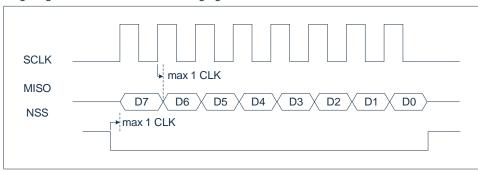

| 19.8.2 SPI Transier ends                                         |         |

| 19.9.1 Master Mode Transmission                                  |         |

| 19.9.2 Slave Mode Transmission                                   |         |

| 19.10 SPI Interrupt                                              |         |

| 19.10.1 Interrupt Mask Register EIE2                             |         |

| 19.10.2 Interrupt Priority Control Register EIP2                 |         |

| 19.10.3 Peripheral Interrupt Flag Bit Register EIF2              |         |

|                                                                  |         |

| 20. I2C Module                                                   |         |

| 20.1 Overview                                                    |         |

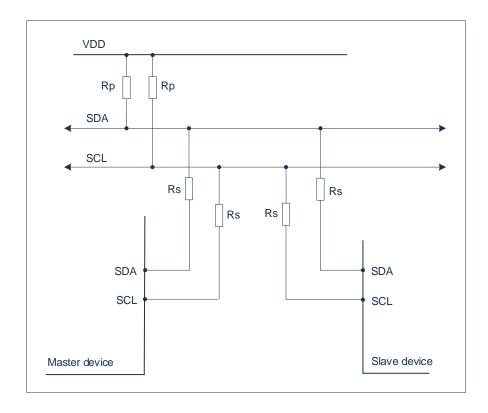

| 20.2 I2C Port Configuration                                      |         |

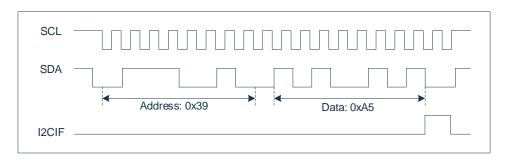

| 20.3 I2C Master Mode                                             |         |

| 20.3.1 I2C Master Mode Timing Cycle Register                     |         |

| 20.3.2 I2C Master Mode Control and Status Registers              |         |

| 20.3.3 I2C Slave Address Register                                |         |

| 20.3.4 I2C Master Mode Transmit and Receive Data Registers       |         |

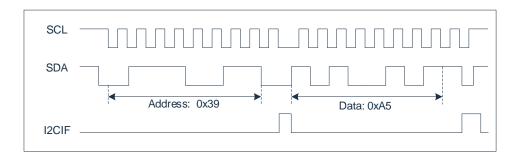

| 20.4 I2C Slave Mode                                              |         |

| 20.7.1 120 OWITAULIESS NEGISIEI 1200ADR                          |         |

|          | I2C Slave Mode Control and Status Registers I2CSCR/I2CSSR    |     |

|----------|--------------------------------------------------------------|-----|

| 20.4.3   | I2C Slave Mode Transmit and Receive Buffer Registers I2CSBUF | 175 |

| 20.5     | C Interrupt                                                  | 176 |

| 20.5.1   | Interrupt Mask Register EIE2                                 | 176 |

| 20.5.2   | Interrupt Priority Control Register EIP2                     | 177 |

| 20.5.3   | Peripheral Interrupt Flag Bit Register EIF2                  | 178 |

| 20.6 I2  | C Slave Mode Transmission Mode                               | 179 |

| 20.6.1   | Single Receive                                               | 179 |

| 20.6.2   | Single send                                                  | 179 |

| 20.6.3   | Continuous reception                                         | 180 |

| 20.6.4   | Continuous Sending                                           | 181 |

| 21. UAR  | T0 Module                                                    | 182 |

| 21.1 O   | verview                                                      | 182 |

| 21.2 U   | ART0 Port Configuration                                      | 182 |

| 21.3 U   | ART0 Baud Rate                                               | 183 |

| 21.3.1   | Baud Rate Clock Source                                       | 183 |

| 21.3.2   | Baud Rate Calculation                                        | 183 |

| 21.3.3   | Baud Rate Error                                              | 184 |

| 21.4 U   | ART0 Register                                                | 186 |

| 21.4.1   | UART0 Baud Rate Selection Register FUNCCR                    | 186 |

| 21.4.2   | UART0 Buffer Register SBUF0                                  | 186 |

| 21.4.3   | UART Control Register SCON0                                  | 187 |

| 21.4.4   | PCON Registers                                               | 188 |

| 21.5 U   | ART0 Interrupt                                               | 189 |

| 21.5.1   | Interrupt Mask Register IE                                   | 189 |

| 21.5.2   | Interrupt Priority Control Register IP                       | 190 |

| 21.5.3   | Interrupt Priority Register EIP3                             | 190 |

| 21.6 U   | ART0 Mode                                                    | 191 |

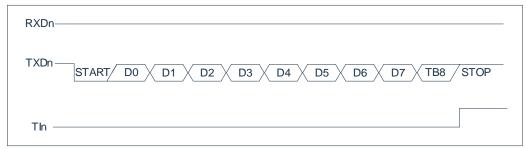

| 21.6.1   | Mode 0 - Synchronous Mode                                    | 191 |

| 21.6.2   | Mode 1-8 Bit Asynchronous Mode (Variable Baud Rate).         | 191 |

| 21.6.3   | Mode 2-9 Bit Asynchronous Mode (Fixed Baud Rate).            | 192 |

| 21.6.4   | Mode 3-9 Bit Asynchronous Mode (Variable Baud Rate)          | 192 |

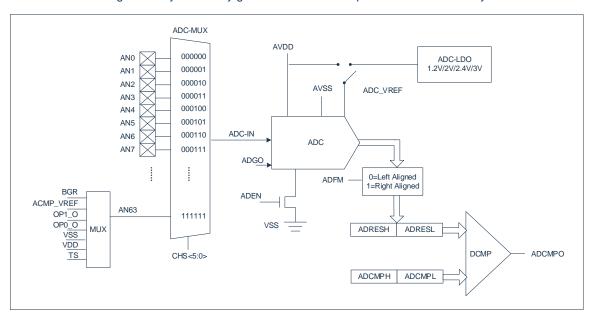

| 22. Anal | og-to-digital Converters (ADCs)                              | 193 |

| 22.1 O   | verview                                                      | 193 |

| 22.2 A   | DC Configuration                                             | 194 |

| 22.2.1   | Port Configuration                                           | 194 |

| 22.2.2   | Channel Selection                                            | 194 |

| 22.2.3   | ADC Reference Voltage                                        | 194 |

| 22.2.4   | Convert the Clock                                            | 195 |

| 22.2.5   | Result Format                                                | 195 |

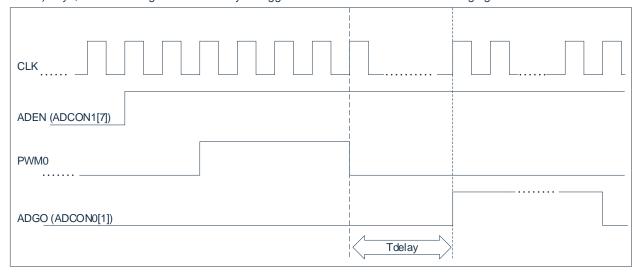

| 22.3 T   | he ADC Hardware Trigger Start                                | 196 |

| 22.3.1   | The External Port Edge Triggers the ADC                      | 196 |

| 22.3.2   | PWM Triggers the ADC                                         | 196 |

| 22.3.3   | Hardware Trigger Start Delay                                 | 196 |

| 22.4 A   | DC Results Comparison                                        | 197 |

| 22.5 H   | ow the ADC Works                                             | 197 |

| 22.5.1   | Start the Conversion                                         | 197 |

| 22.5.2   | Complete the Conversion                                      | 197 |

| 22.5.3   | Terminate the Conversion                                     | 197 |

| 22.5.4   | A/D Conversion Steps                                         | 198 |

| 22.5.5   | Go to sleep during the conversion process                    | 198 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 199                                                                                         |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|

| 22.6.1 AD Control Register ADCON0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 199                                                                                         |

| 22.6.2 AD Control Register ADCON1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 200                                                                                         |

| 22.6.3 AD Control Register ADCON2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 200                                                                                         |

| 22.6.4 AD Channel Selection Register ADCCHS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 201                                                                                         |

| 22.6.5 AD Comparator Control Register ADCPC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 201                                                                                         |

| 22.6.6 AD Hardware Trigger Delay Data Register ADDLYL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                             |

| 22.6.7 AD Data Register High ADRESH, ADFM=0 (Left-aligned).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 202                                                                                         |

| 22.6.8 AD Data Register Low ADRSL, ADFM=0 (Left-aligned)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 202                                                                                         |

| 22.6.9 AD Data Register High ADRESH, ADFM=1 (Right-aligned)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 202                                                                                         |

| 22.6.10 AD Data Register Low ADRSL, ADFM = 1 (Right-aligned)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                             |

| 22.6.11 AD Comparator Data Register ADCMPH                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                             |

| 22.6.12 AD Comparator Data Register ADCMPL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                             |

| 22.6.13 AD Reference Voltage Control Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                             |

| 22.7 ADC Interrupt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                             |

| 22.7.1 Interrupt Mask Register EIE2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                             |

| 22.7.2 Interrupt Priority Control Register EIP2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                             |

| 22.7.3 Peripheral Interrupt Flag Bit Register EIF2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 206                                                                                         |

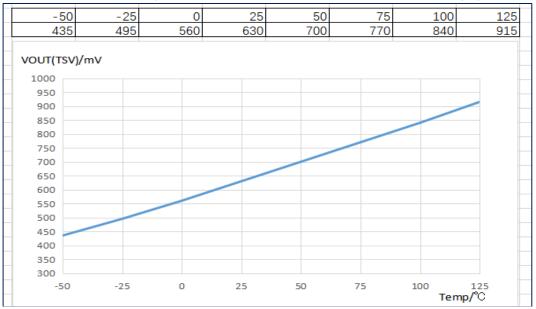

| 23. Temperature Sensor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 207                                                                                         |

| 23.1 Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                             |

| 23.2 Register Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                             |

| 23.2.1 The Temperature Sensor Control Register TS _REG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                             |

| 23.3 Feature Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                             |

| 23.3.1 Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                             |

| 23.3.2 Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                             |

| 23.3.3 Calculation Formula                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                             |

| 23.3.3 Calculation Formula                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                             |

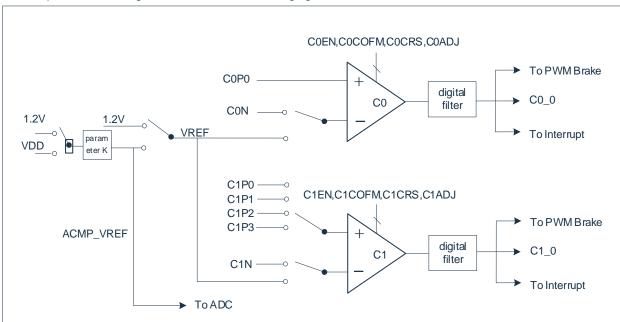

| 24. Analog Comparator (ACMP0/1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 209                                                                                         |

| 24. Analog Comparator (ACMP0/1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | <b>209</b>                                                                                  |

| 24. Analog Comparator (ACMP0/1).  24.1 Comparator Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | <b>209</b>                                                                                  |

| 24. Analog Comparator (ACMP0/1).  24.1 Comparator Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                             |

| 24. Analog Comparator (ACMP0/1).  24.1 Comparator Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                             |

| 24. Analog Comparator (ACMP0/1).  24.1 Comparator Features.  24.2 Comparator Structure.  24.3 Related Registers.  24.3.1 Comparator Control Register CnCON0.  24.3.2 Comparator Control Register CnCON1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                             |

| 24. Analog Comparator (ACMP0/1).  24.1 Comparator Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                             |

| 24. Analog Comparator (ACMP0/1).  24.1 Comparator Features.  24.2 Comparator Structure.  24.3 Related Registers.  24.3.1 Comparator Control Register CnCON0.  24.3.2 Comparator Control Register CnCON1.  24.3.3 Comparator Control Register CnCON2.  24.3.4 Comparator Adjustment Bit Selection Register CnADJE.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                             |

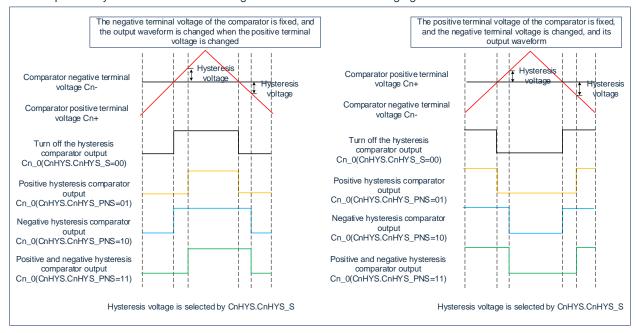

| 24. Analog Comparator (ACMP0/1).  24.1 Comparator Features.  24.2 Comparator Structure.  24.3 Related Registers.  24.3.1 Comparator Control Register CnCON0.  24.3.2 Comparator Control Register CnCON1.  24.3.3 Comparator Control Register CnCON2.  24.3.4 Comparator Adjustment Bit Selection Register CnADJE.  24.3.5 Comparator Hysteresis Control Register CnHYS.                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                             |

| 24. Analog Comparator (ACMP0/1).  24.1 Comparator Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                             |

| 24. Analog Comparator (ACMP0/1).  24.1 Comparator Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                             |

| 24. Analog Comparator (ACMP0/1).  24.1 Comparator Features.  24.2 Comparator Structure.  24.3 Related Registers.  24.3.1 Comparator Control Register CnCON0.  24.3.2 Comparator Control Register CnCON1.  24.3.3 Comparator Control Register CnCON2.  24.3.4 Comparator Adjustment Bit Selection Register CnADJE.  24.3.5 Comparator Hysteresis Control Register CnHYS.  24.3.6 Comparator Reference Voltage Control Register CNVRCON.  24.3.7 Comparator Brake Control Register CNFBCON.                                                                                                                                                                                                                                                                                                                        |                                                                                             |

| 24. Analog Comparator (ACMP0/1).  24.1 Comparator Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 209 209 209 211 211 211 212 212 213 214 215                                                 |

| 24. Analog Comparator (ACMP0/1).  24.1 Comparator Features 24.2 Comparator Structure.  24.3 Related Registers.  24.3.1 Comparator Control Register CnCON0.  24.3.2 Comparator Control Register CnCON1.  24.3.3 Comparator Control Register CnCON2.  24.3.4 Comparator Adjustment Bit Selection Register CnADJE.  24.3.5 Comparator Hysteresis Control Register CnHYS.  24.3.6 Comparator Reference Voltage Control Register CNVRCON.  24.3.7 Comparator Brake Control Register CNFBCON.  24.4 Comparator Interrupt.  24.4.1 Interrupt Priority Control Register EIP1.  24.4.2 Comparator Interrupt Mask Register CNIE.                                                                                                                                                                                           | 209 209 209 211 211 211 212 212 213 214 215 215                                             |

| 24. Analog Comparator (ACMP0/1).  24.1 Comparator Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 209 209 209 211 211 211 212 212 213 214 215 215 216                                         |

| 24. Analog Comparator (ACMP0/1).  24.1 Comparator Features 24.2 Comparator Structure.  24.3 Related Registers.  24.3.1 Comparator Control Register CnCON0.  24.3.2 Comparator Control Register CnCON1.  24.3.3 Comparator Control Register CnCON2.  24.3.4 Comparator Adjustment Bit Selection Register CnADJE.  24.3.5 Comparator Hysteresis Control Register CnHYS.  24.3.6 Comparator Reference Voltage Control Register CNVRCON.  24.3.7 Comparator Brake Control Register CNFBCON.  24.4 Comparator Interrupt.  24.4.1 Interrupt Priority Control Register EIP1.  24.4.2 Comparator Interrupt Mask Register CNIE.                                                                                                                                                                                           | 209 209 209 211 211 211 212 212 213 214 215 215 216                                         |

| 24. Analog Comparator (ACMP0/1).  24.1 Comparator Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 209 209 209 211 211 211 212 212 213 214 215 215 216 217                                     |

| 24. Analog Comparator (ACMP0/1).  24.1 Comparator Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 209 209 209 211 211 211 212 212 213 214 215 216 216 217                                     |

| 24. Analog Comparator (ACMP0/1).  24.1 Comparator Features.  24.2 Comparator Structure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 209 209 209 211 211 211 212 212 213 214 215 215 216 217 217                                 |

| 24. Analog Comparator (ACMP0/1).  24.1 Comparator Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                             |

| 24.1 Comparator Features 24.2 Comparator Structure 24.3 Related Registers 24.3.1 Comparator Control Register CnCON0 24.3.2 Comparator Control Register CnCON1 24.3.3 Comparator Control Register CnCON2 24.3.4 Comparator Adjustment Bit Selection Register CnADJE 24.3.5 Comparator Hysteresis Control Register CnHYS 24.3.6 Comparator Reference Voltage Control Register CNVRCON 24.3.7 Comparator Brake Control Register CNFBCON 24.4.1 Interrupt Priority Control Register EIP1 24.4.2 Comparator Interrupt Mask Register CNIE 24.4.3 Comparator Interrupt Flag Register CNIE 25.5 Flash Memory 25.1 Overview 25.2 Related Registers 25.2.1 FLASH Protect Lock Register MLOCK                                                                                                                               | 209 209 209 211 211 211 212 212 213 214 215 216 216 217 218                                 |

| 24.1 Comparator Features 24.2 Comparator Structure 24.3 Related Registers 24.3.1 Comparator Control Register CnCON0 24.3.2 Comparator Control Register CnCON1 24.3.3 Comparator Control Register CnCON2 24.3.4 Comparator Adjustment Bit Selection Register CnADJE 24.3.5 Comparator Hysteresis Control Register CnHYS 24.3.6 Comparator Reference Voltage Control Register CNVRCON 24.3.7 Comparator Brake Control Register CNFBCON 24.4.1 Interrupt Priority Control Register EIP1 24.4.2 Comparator Interrupt Mask Register CNIE 24.4.3 Comparator Interrupt Flag Register CNIE 25.4 Related Registers 25.2 Related Registers 25.2.1 FLASH Protect Lock Register MLOCK 25.2.2 FLASH Memory Data Register MDATA                                                                                                |                                                                                             |

| 24.1 Comparator Features  24.2 Comparator Structure  24.3 Related Registers  24.3.1 Comparator Control Register CnCON0  24.3.2 Comparator Control Register CnCON1  24.3.3 Comparator Control Register CnCON2  24.3.4 Comparator Adjustment Bit Selection Register CnADJE  24.3.5 Comparator Hysteresis Control Register CnHYS  24.3.6 Comparator Reference Voltage Control Register CNVRCON  24.3.7 Comparator Brake Control Register CNFBCON  24.4 Comparator Interrupt  24.4.1 Interrupt Priority Control Register EIP1  24.4.2 Comparator Interrupt Mask Register CNIE  24.4.3 Comparator Interrupt Flag Register CNIE  25.4 Flash Memory  25.1 Overview  25.2 Related Registers  25.2.1 FLASH Protect Lock Register MLOCK  25.2.2 FLASH Memory Address Register MADRL                                        | 209 209 209 211 211 211 212 212 213 214 215 215 216 216 218 218 218                         |

| 24.1 Comparator Features  24.2 Comparator Structure  24.3 Related Registers  24.3.1 Comparator Control Register CnCON0  24.3.2 Comparator Control Register CnCON1  24.3.3 Comparator Control Register CnCON2  24.3.4 Comparator Adjustment Bit Selection Register CnADJE  24.3.5 Comparator Hysteresis Control Register CnHYS  24.3.6 Comparator Reference Voltage Control Register CNVRCON  24.3.7 Comparator Brake Control Register CNFBCON  24.4.1 Interrupt Priority Control Register EIP1  24.4.2 Comparator Interrupt Mask Register CNIE  24.4.3 Comparator Interrupt Flag Register CNIE  25.1 Overview  25.2 Related Registers  25.2.1 FLASH Protect Lock Register MLOCK  25.2.2 FLASH Memory Data Register MDATA  25.2.3 FLASH Memory Address Register MADRL  25.2.4 FLASH Memory Address Register MADRH | 209 209 209 211 211 211 212 212 213 214 215 216 216 217 218 218 218 218 218 218 218 218 218 |

| 25.3         | Feature Description                       | 220        |

|--------------|-------------------------------------------|------------|

| 26. Un       | nique ID (UID)                            | 220        |

|              | Overview                                  |            |

| 27. Us       | ser configuration                         | 224        |

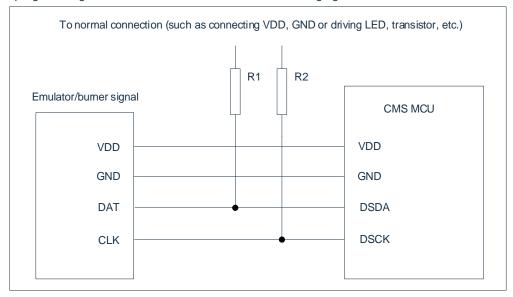

| 28. ln-      | circuit Programming and Debugging         | 226        |

| 28.1<br>28.2 | Online Programming Mode Online Debug Mode | 226        |

| 29. lns      | struction description                     | 228        |

| 29.1<br>29.2 | Symbol description                        | 228<br>229 |

| 30. Ve       | rsion Revision Notes                      | 232        |

|              |                                           |            |

# 1. Central Processing Unit (CPU)

The series is a microcontroller with 8-bit 8051 frame structure. The CPU is the core component of the microcontroller, which is composed of arithmetic units, controllers, and special register groups. The arithmetic unit module mainly implements data arithmetic and logic operations, bit variable processing and data transfer operations; the controller module mainly decodes instructions, and then sends out various control signals; the special register group is mainly used to indicate the memory address of the current instruction to be executed, Store the operand and indicate the state after the instruction is executed. The special register group mainly includes accumulatorACC, general register B, stack pointer SP, data pointer DPTR, Program status registerPSW, Program counterPC, etc.

#### 1.1 Reset Vector (0000H)